AMAG nanometro

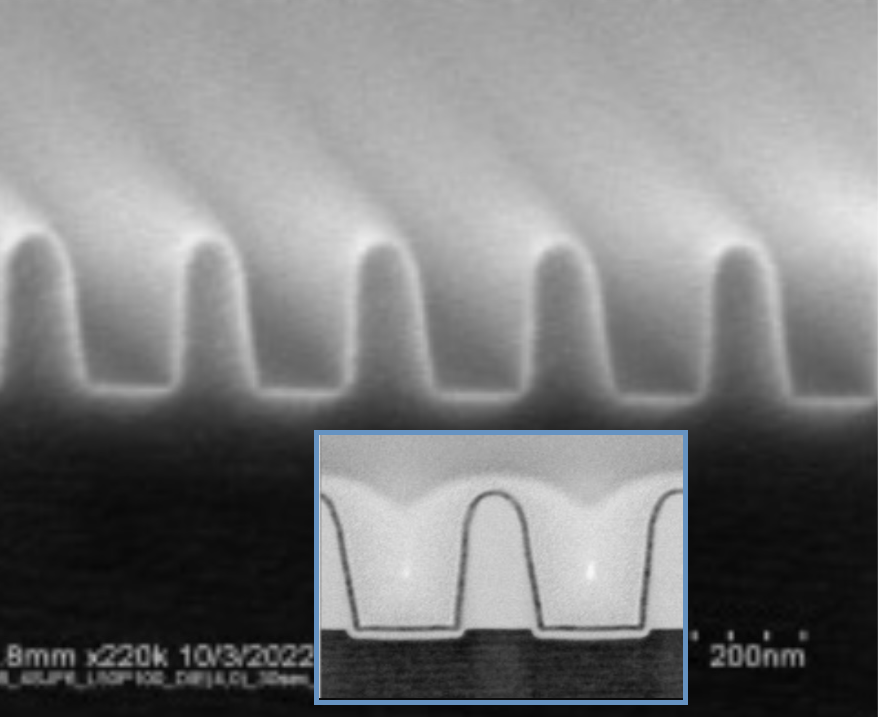

Chip-AMAG7 Hardmask LineSpace, 100 nm depth, L50P100 anchor target w/TiN anti-charge coating

Chip-AMAG7 Hardmask LineSpace, 100 nm depth, L50P100 anchor target w/TiN anti-charge coating

AMAG7 LineSpace module etched into 100 nm SiO2 on Si, terminating on Si substrate. The anchor target is L50P100, downsized to L47P100.

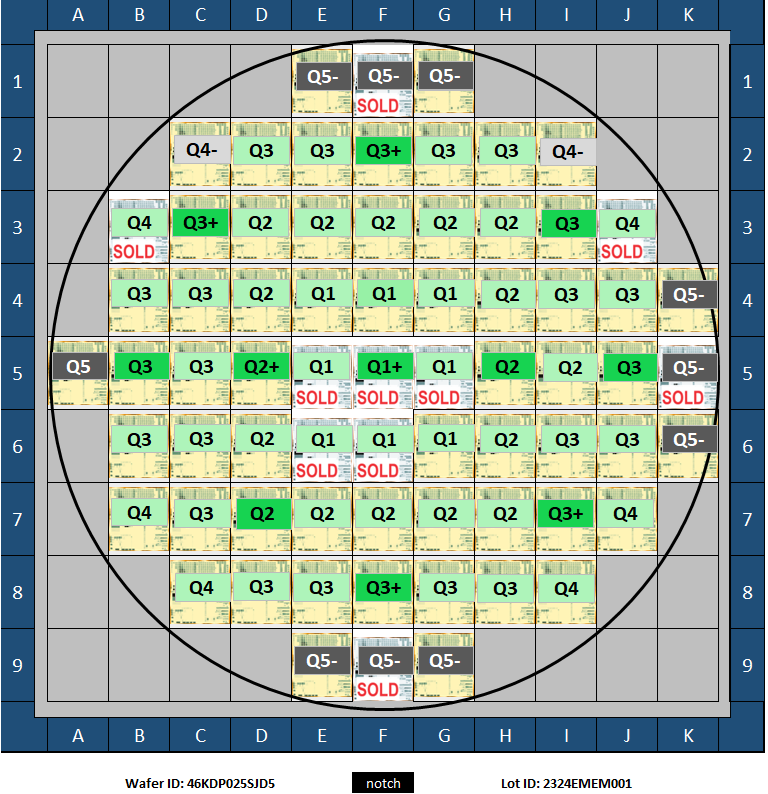

| Chip | 27mm x 33mm |

| Process | AMAG7, L50P100 LineSpace, 100 nm depth, ALD 30A TiN coating |

| Stack | 100 nm SiO2 on Si, lines etched in SiO2, terminate on Si substrate |

| Depth | 100 nm |

| Pattern | AMAG7, Full Field, 27 mm x 33 mm, 66 die plus 10 partial die |

| Anchor target | L50P100 downsized to L47P100 |

| Imaged targets | L50P100, L52P104, L55P110, L60P120, C120 Faux Memory |

| CD, Anchor Target | Bottom CD: ~47 nm |

| Reference metrology |

Anchor target: CD measurements & images,all sites/wafer. Reports: "100nm depth oxide HM (L50P100) Line & Space, navigation & results": "100nm depth oxide HM (L50P100) Line & Space, with 30A ALD TiN Coating,navigation & results": |

Regular price

Regular price

Sale price

Unit price

per

Couldn't load pickup availability